# **GN412x PCI Express**

**Family Reference Manual**

# **Revision History**

| Version | ECR    | Date      | Changes and Modifications |

|---------|--------|-----------|---------------------------|

| 0       | 151928 | June 2009 | New document.             |

### Contents

| 1. Introduction                                         |    |

|---------------------------------------------------------|----|

| 1.1 Features                                            |    |

| 1.2 Live on Power-up                                    | 13 |

| 1.3 FPGA On-the-Fly Configuration Loader                |    |

| 1.4 Local Bus Interface                                 |    |

| 1.5 Virtual Channel Support                             |    |

| 1.6 PCI Express Application Layer                       | 14 |

| 1.7 Interrupt Controller                                |    |

| 1.8 2-Wire Serial Controller                            |    |

| 1.9 How to Use this Family Reference Manual             | 15 |

| 1.9.1 Family Reference Manual Conventions               |    |

| 1.10 Getting Help from Gennum                           |    |

| 1.11 Getting Answers to PCI Express Related Questions   |    |

| 2. Overview                                             |    |

| 2.1 GN412x Signals                                      |    |

| 3. Initialization                                       | 20 |

| 3.1 Reset Initialization                                | 20 |

| 3.1.1 Initializing the Internal Registers               | 21 |

| 3.1.2 Selecting an Initialization Mode                  | 21 |

| 3.1.3 Initialization from a 2-Wire EEPROM               | 22 |

| 3.1.4 Initialization Using a Local Processor            | 25 |

| 3.1.5 Initialization Using the PCIe Configuration Space |    |

| 3.2 OS Initialization                                   |    |

| 3.3 PCI Express Configuration Space Initialization      |    |

| 3.4 Clock Configuration                                 |    |

| 3.4.1 PCI Express Clock                                 |    |

| 3.4.2 Local Clock                                       | 27 |

| 4. PCI Express Link                                     |    |

| 4.1 Physical Interface                                  |    |

| 4.1.1 Signal Polarity Inversion                         |    |

| 4.1.2 PCI Express CEM Signals                           | 32 |

| 4.1.3 PCI Express PHY Control                           |    |

| 4.2 PCI Express Traffic Routing                         |    |

GN412x PCI Express Family Reference Manual 52624 - 0 June 2009

| 4.3 Configuration Space                             |    |

|-----------------------------------------------------|----|

| 4.3.1 Type 0 PCI Configuration Space                |    |

| 4.3.2 PCI Express Capability                        |    |

| 4.3.3 Power Management Capability                   |    |

| 4.3.4 Device Serial Number Capability               |    |

| 4.3.5 Virtual Channel Capability                    |    |

| 4.3.6 MSI Capability                                |    |

| 4.4 Bridge Operation                                |    |

| 4.4.1 Flow Control                                  |    |

| 5. Local Bus Interface                              |    |

| 5.1 Local Bus Signals                               |    |

| 5.1.1 L2P DDR Source Synchronous Signals            |    |

| 5.1.2 P2L DDR Source Synchronous Signals            |    |

| 5.1.3 Signal Naming Conventions                     |    |

| 5.1.4 Local Bus Clocking                            |    |

| 5.1.5 Local Bus Control Signals                     |    |

| 5.1.6 Signals for Inbound Dataflow (PCIe-to-Local)  |    |

| 5.1.7 Signals for Outbound Dataflow (Local-to-PCIe) |    |

| 5.2 Local Bus Protocol                              |    |

| 5.2.1 Header Format                                 |    |

| 5.2.2 PCI Express Target Transactions               |    |

| 5.2.3 PCI Express Master Transactions               |    |

| 6. Interrupt Control Unit                           |    |

| 6.1 Overview                                        |    |

| 6.2 Operation                                       |    |

| 7. Peripherals                                      |    |

| 7.1 2-Wire Interface                                |    |

| 7.1.1 Master Mode                                   |    |

| 7.1.2 Slave Mode                                    |    |

| 7.1.3 2-Wire Interface Additional Information       |    |

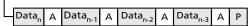

| 7.2 General Purpose IO Block                        |    |

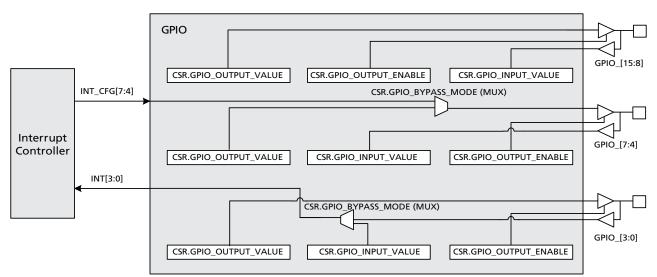

| 8. FPGA Configuration Loader                        |    |

| 8.1 Overview                                        |    |

| 8.2 Operation                                       |    |

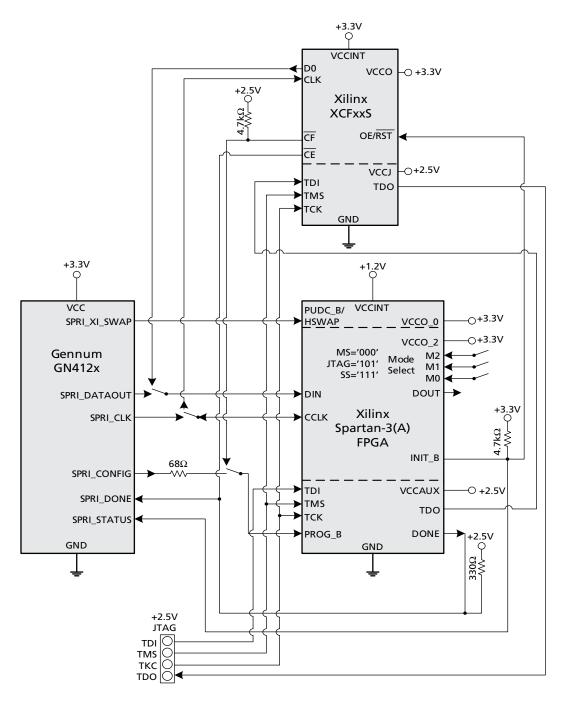

| 8.3 Xilinx FPGA Configuration                       |    |

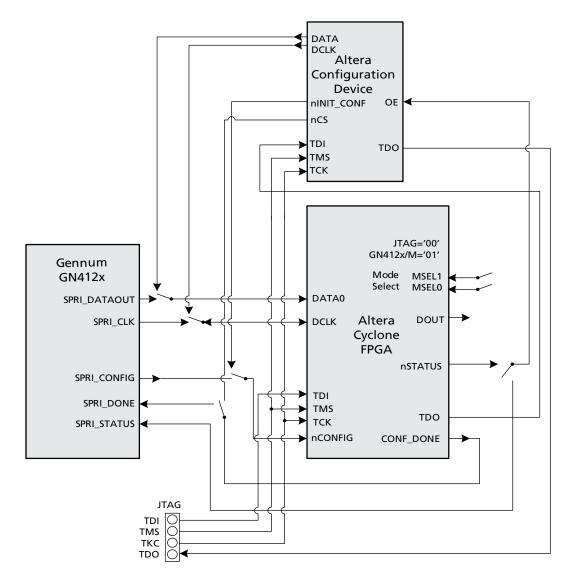

| 8.4 Altera FPGA Configuration                       |    |

| 8.5 FCL Programming                                 | 75 |

| 8.5.1 FCL Register Map                              |    |

| 8.5.2 GPIO FPGA Configuration                       |    |

| 8.5.3 FCL FPGA Configuration                        |    |

| 8.5.4 FCL FSM FPGA Configuration                    |    |

| 8.6 Additional information                          | 79 |

| 9. Device Application                               |    |

| 9.1 PCI Express Reference Clock Routing             |    |

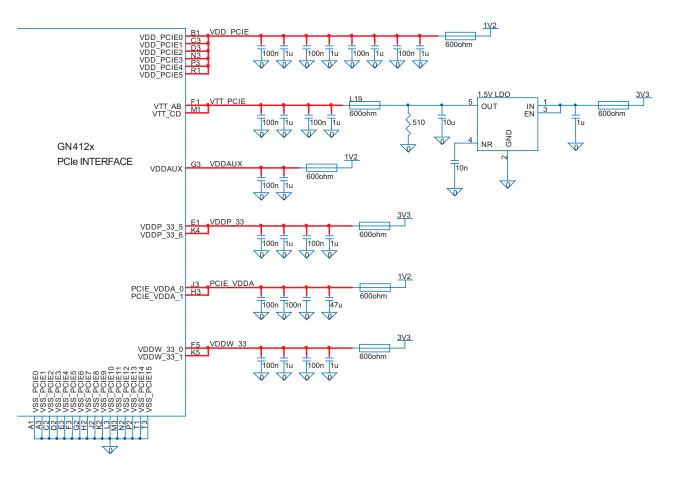

| 9.2 PCI Express Power Supply Distribution           |    |

GN412x PCI Express Family Reference Manual 52624 - 0 June 2009

| 10. Internal Registers                                                           |

|----------------------------------------------------------------------------------|

| 10.1 Internal Register Access Modes 82                                           |

| 10.1.1 PCI Express Configuration Access                                          |

| 10.1.2 PCI Express BAR4 Access 82                                                |

| 10.1.3 2-Wire Access                                                             |

| 10.2 Register Conventions                                                        |

| 10.2.1 Register Bit Types                                                        |

| 10.2.2 Numbering Conventions                                                     |

| 10.2.3 Reserved Register Bits                                                    |

| 10.3 Register Map                                                                |

| 10.4 Register Descriptions                                                       |

| 10.4.1 PCI Type 0 Configuration Header Registers and Related Control Registers 8 |

| 10.4.2 Power Management Capability Registers                                     |

| 10.4.3 Message Signalled Interrupt Registers                                     |

| 10.4.4 PCI Express Capability Registers                                          |

| 10.4.5 Device Serial Number Registers116                                         |

| 10.4.6 Virtual Channel Capability Registers                                      |

| 10.4.7 GN412x System Registers125                                                |

| 10.4.8 2-Wire Interface Registers                                                |

| 10.4.9 GPIO Registers146                                                         |

| 10.4.10 FPGA Configuration Loader Registers                                      |

# **List of Figures**

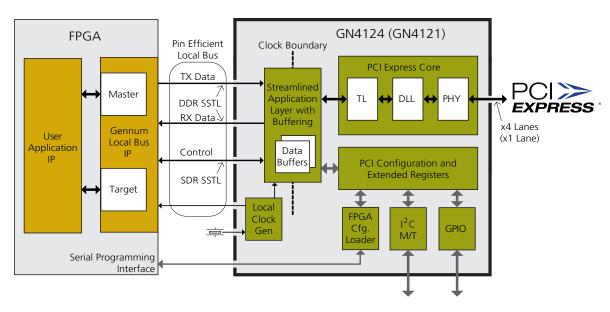

| Figure 1-1: GN412x with FPGA Simplified Block Diagram                            | 12 |

|----------------------------------------------------------------------------------|----|

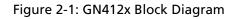

| Figure 2-1: GN412x Block Diagram                                                 | 18 |

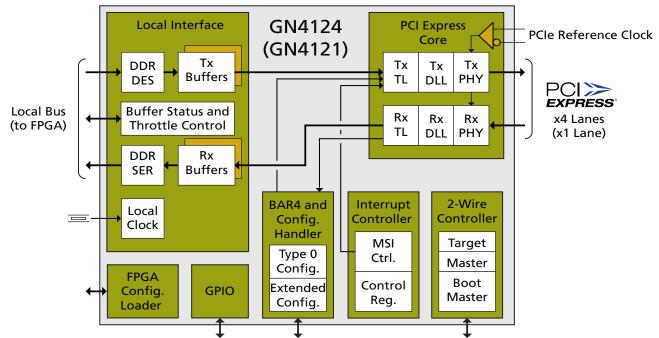

| Figure 2-2: GN412x Signal Groups Diagram                                         | 19 |

| Figure 3-1: Reset Input and Output Operation                                     |    |

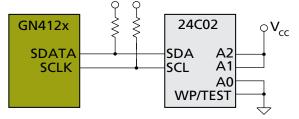

| Figure 3-2: Serial EEPROM Initialization Schematics                              | 25 |

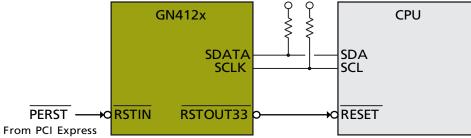

| Figure 3-3: Connection for Initialization Using the Local Processor              | 26 |

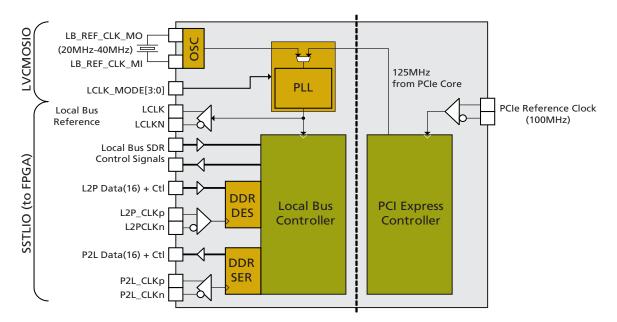

| Figure 3-4: GN412x Device Clocking                                               | 27 |

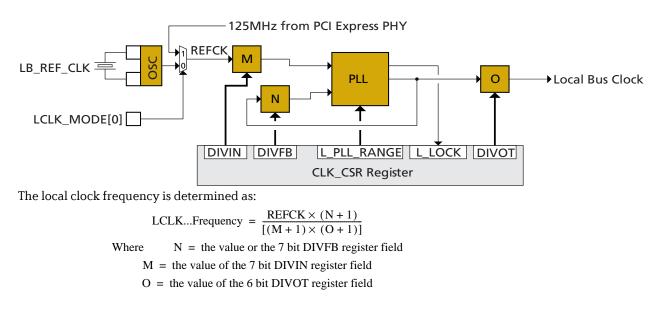

| Figure 3-5: GN412x Local Bus Clock Generation PLL                                | 28 |

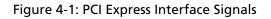

| Figure 4-1: PCI Express Interface Signals                                        | 31 |

| Figure 4-2: Internal Register Space                                              | 34 |

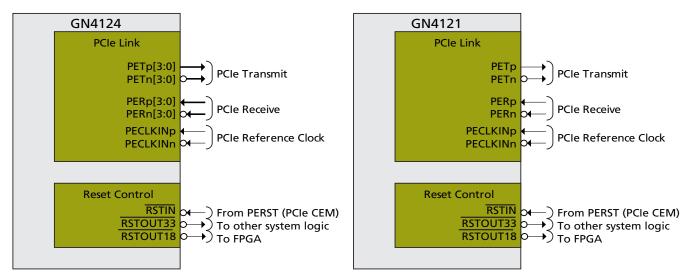

| Figure 5-1: Local Bus Interface Signals                                          | 40 |

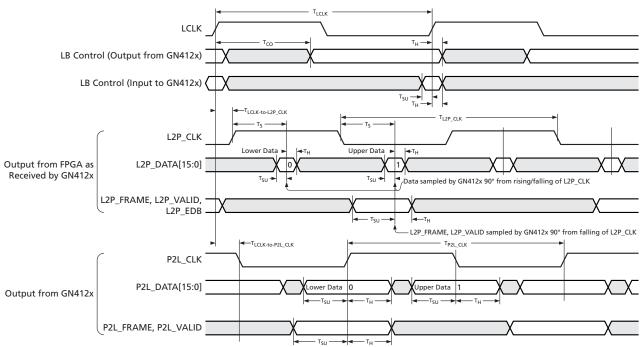

| Figure 5-2: Local Bus Timing                                                     | 41 |

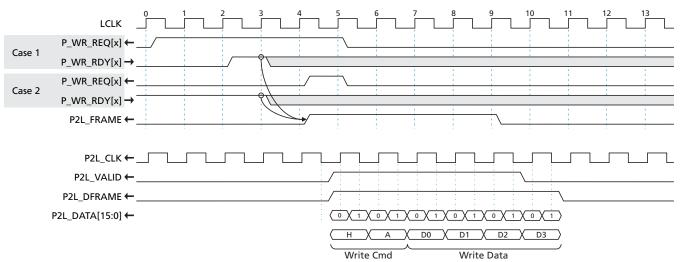

| Figure 5-3: PCIe to Local Bus Target Write Transaction                           | 52 |

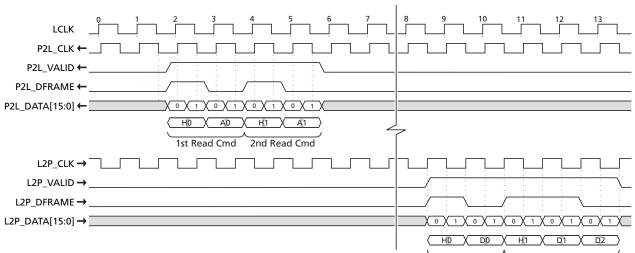

| Figure 5-4: PCIe to Local Bus Target Read Transaction                            | 53 |

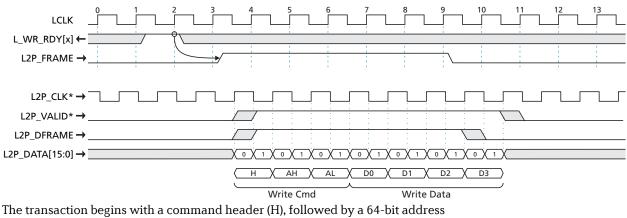

| Figure 5-5: Local-to-PCIe Master Write Transaction                               | 54 |

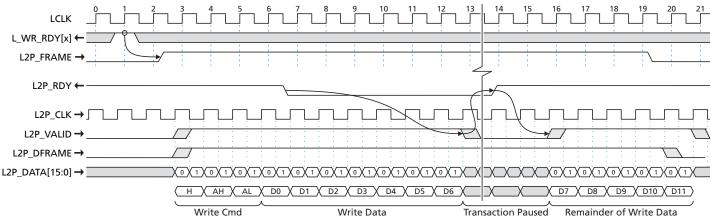

| Figure 5-6: Operation of the L2P_RDY Signal During an L2P Transaction            | 55 |

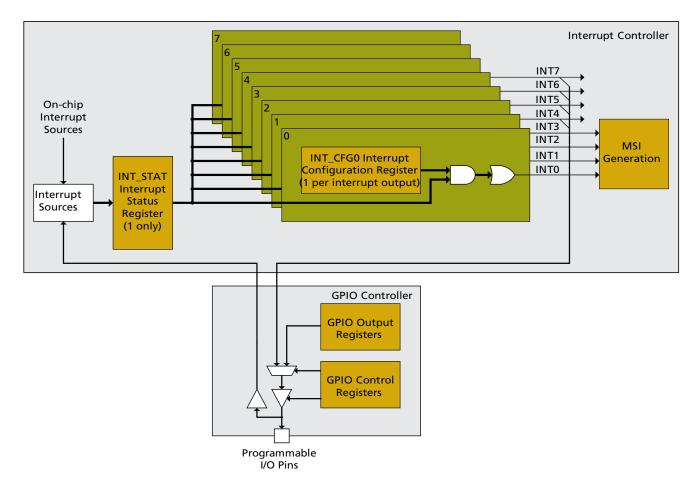

| Figure 6-1: Interrupt Controller Block Diagram                                   | 57 |

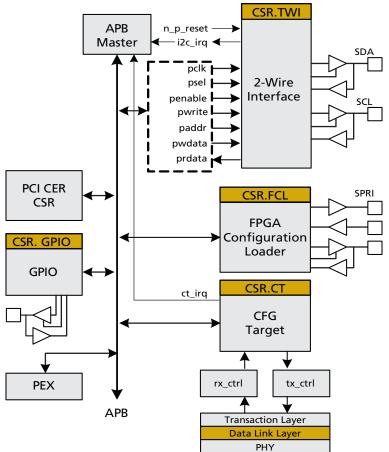

| Figure 7-1: APB and Peripheral Devices Block Diagram                             | 59 |

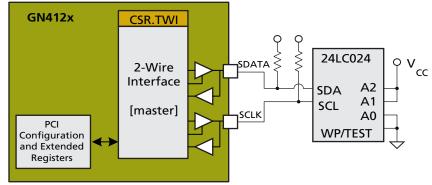

| Figure 7-2: 2-Wire Interface in Master Mode                                      | 61 |

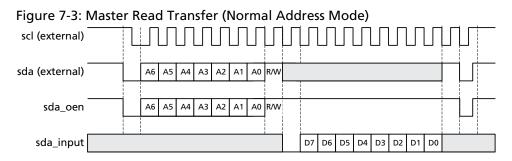

| Figure 7-3: Master Read Transfer (Normal Address Mode)                           | 61 |

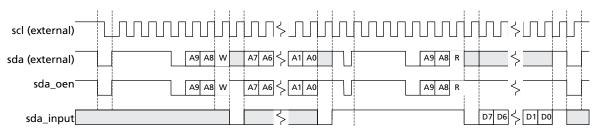

| Figure 7-4: Master Read Transfer (Extended Address Mode)                         | 61 |

| Figure 7-5: Master Byte Read                                                     | 63 |

| Figure 7-6: Master Page Read                                                     | 63 |

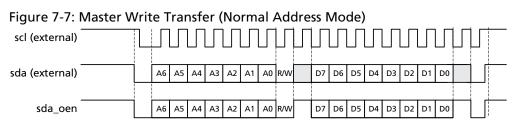

| Figure 7-7: Master Write Transfer (Normal Address Mode)                          | 63 |

| Figure 7-8: Master Write Transfer (Extended Address Mode)                        | 63 |

| Figure 7-9: Master Byte Write                                                    | 64 |

| Figure 7-10: Master Page Write                                                   |    |

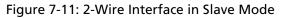

| Figure 7-11: 2-Wire Interface in Slave Mode                                      | 65 |

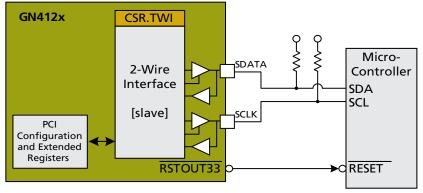

| Figure 7-12: Slave Double Word Read                                              | 66 |

| Figure 7-13: Slave Double Word Page Read                                         | 66 |

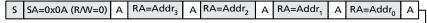

| Figure 7-14: Slave Double Word Write                                             | 67 |

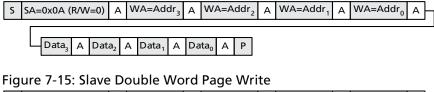

| Figure 7-15: Slave Double Word Page Write                                        | 67 |

| Figure 7-16: GPIO Block Diagram                                                  | 68 |

| Figure 8-1: FPGA Configuration Loader Block Diagram.                             | 71 |

| Figure 8-2: Serial Programming Interface: Xilinx Spartan-3(A) and Platform Flash |    |

| example.                                                                         |    |

| Figure 8-3: Serial Programming Interface: Altera Cyclone example.                |    |

| Figure 9-1: PCI Express Related Power Supply Design                              | 81 |

# **List of Tables**

| Table 3-1: Initialization Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ζ1                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3-2: Serial EEPROMs Compatible with the GN412x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                                                                                                                                                             |

| Table 3-3: EEPROM Interpretation by the GN412x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                                                                                                                             |

| Table 3-4: Address Format for EEPROM Interpretation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                |

| Table 3-5: GN412x Clock Selection and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                |

| Table 4-1: Flow Control Credits Advertised by the GN412x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                |

| Table 5-1: Signals for Inbound PCIe to Local Packet Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                |

| Table 5-2: Signals for Outbound Local to PCIe Packet Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                |

| Table 5-3: Summary of Local Bus Transaction Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                |

| Table 5-4: Header Format for P2L Writes (Target Writes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                |

| Table 5-5: Header Format for P2L Read Requests (Target Read Request)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                |

| Table 5-6: Header Format for L2P Read Completions (Master Read Completion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                |

| Without Data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                                                                                                                                                                             |

| Table 5-7: Header Format for L2P Read Completions (Master Read Completion With Data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48                                                                                                                                                                                             |

| Table 5-8: Header Format for L2P Writes (32 bit Address Specified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48                                                                                                                                                                                             |

| Table 5-9: Header Format for L2P Writes (64 bit Address Specified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49                                                                                                                                                                                             |

| Table 5-10: Header Format for L2P Read Requests (32 bit Address Specified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                                                                                                                                                                             |

| Table 5-11: Header Format for L2P Read Requests (64 bit Address Specified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                                                                                                                                                                             |

| Table 5-12: Header Format for P2L Read Completions (Target Read Completion Without Data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49                                                                                                                                                                                             |

| Table 5-13: Header Format for P2L Read Completions (Target Read Completion With Data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                |

| Table 5-14: Local Bus Header Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                                                                                             |

| Table 7-1: 2-Wire Interface Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60                                                                                                                                                                                             |

| Table 7-2: GPIO Definition (when bypass mode is enabled via GPIO_BYPASS_MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                |

| register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                |

| register)<br>Table 8-1: FCL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71                                                                                                                                                                                             |

| register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71                                                                                                                                                                                             |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71<br>76<br>84                                                                                                                                                                                 |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71<br>76<br>84                                                                                                                                                                                 |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71<br>76<br>84<br>84<br>89                                                                                                                                                                     |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71<br>76<br>84<br>84<br>89<br>89                                                                                                                                                               |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD                                                                                                                                                                                                                                                                                                                                                                                                                        | 71<br>76<br>84<br>84<br>89<br>89<br>89                                                                                                                                                         |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71<br>76<br>84<br>84<br>89<br>89<br>89                                                                                                                                                         |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD                                                                                                                                                                                                                                                                                                                                                                                                                        | 71<br>76<br>84<br>89<br>89<br>89<br>89                                                                                                                                                         |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT                                                                                                                                                                                                                                                                                                                                                                                                | 71<br>76<br>84<br>89<br>89<br>89<br>91<br>92                                                                                                                                                   |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE.<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION                                                                                                                                                                                                                                                                                                                                         | 71<br>76<br>84<br>89<br>89<br>89<br>91<br>92<br>92                                                                                                                                             |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE                                                                                                                                                                                                                                                                                                            | 71<br>76<br>84<br>89<br>89<br>89<br>91<br>92<br>92                                                                                                                                             |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE                                                                                                                                                                                                                                                            | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>92</li> <li>93</li> </ul>                                                 |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE.<br>Table 10-10: PCI_LATENCY.                                                                                                                                                                                                                              | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> </ul>                                                 |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE.<br>Table 10-5: PCI_CMD<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE<br>Table 10-10: PCI_LATENCY.<br>Table 10-11: PCI_HEADER                                                                                                                                                                                                                             | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>93</li> </ul>                                     |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE.<br>Table 10-5: PCI_CMD<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE.<br>Table 10-10: PCI_LATENCY<br>Table 10-11: PCI_HEADER<br>Table 10-12: PCI_BIST                                                                                                                                                  | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> </ul>                                     |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE<br>Table 10-10: PCI_LATENCY<br>Table 10-11: PCI_HEADER<br>Table 10-12: PCI_BIST<br>Table 10-13: PCI_BAR0_LOW                                                                                                                  | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> </ul>                                     |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE<br>Table 10-10: PCI_LATENCY<br>Table 10-11: PCI_HEADER<br>Table 10-12: PCI_BIST<br>Table 10-13: PCI_BAR0_LOW<br>Table 10-14: PCI_BAR0_HIGH                                                                                     | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> </ul>             |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE.<br>Table 10-9: PCI_CACHE.<br>Table 10-10: PCI_LATENCY<br>Table 10-11: PCI_HEADER.<br>Table 10-12: PCI_BIST.<br>Table 10-13: PCI_BAR0_LOW<br>Table 10-14: PCI_BAR0_LOW                                                         | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> <li>97</li> </ul>             |

| register)<br>Table 8-1: FCL Interface<br>Table 8-2: FCL Register Map<br>Table 10-1: Description of Register Bit Types<br>Table 10-2: Register Map<br>Table 10-3: PCI_VENDOR<br>Table 10-3: PCI_VENDOR<br>Table 10-4: PCI_DEVICE<br>Table 10-5: PCI_CMD<br>Table 10-5: PCI_CMD<br>Table 10-6: PCI_STAT<br>Table 10-7: PCI_REVISION<br>Table 10-7: PCI_REVISION<br>Table 10-8: PCI_CLASS_CODE<br>Table 10-9: PCI_CACHE<br>Table 10-9: PCI_CACHE<br>Table 10-10: PCI_LATENCY<br>Table 10-11: PCI_HEADER<br>Table 10-12: PCI_BIST<br>Table 10-13: PCI_BAR0_LOW<br>Table 10-14: PCI_BAR0_HIGH<br>Table 10-15: PCI_BAR2_LOW<br>Table 10-16: PCI_BAR2_HIGH | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> <li>97</li> <li>97</li> </ul> |

| register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> <li>97</li> <li>98</li> </ul>             |

| register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>71</li> <li>76</li> <li>84</li> <li>89</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> <li>97</li> <li>98</li> <li>98</li> </ul> |

| Table 10-22: PCI ROM BASE                               | 00 |

|---------------------------------------------------------|----|

| Table 10-23: PM_CAP_POINTER                             |    |

| Table 10-24: PCI_INT_LINE                               |    |

| Table 10-25: PCI_INT_PIN                                |    |

| Table 10-26: PCI_MIN_GNT                                |    |

| Table 10-27: PCI_MAX_LAT                                |    |

| Table 10-28: PM_CAP_ID                                  |    |

| Table 10-29: PM_NEXT_ID                                 |    |

| Table 10-20: PM_CAP                                     |    |

| Table 10-31: PM_CSR                                     |    |

| Table 10-32: PM_CSR_BSE                                 |    |

| Table 10-33: PM_DATA                                    |    |

| Table 10-34: MSI_CAP_ID                                 |    |

| Table 10-35: MSI_NEXT_ID                                |    |

| Table 10-36: MSI_CONTROL                                |    |

| Table 10-37: MSI_ADDRESS_LOW                            |    |

| Table 10-38: MSI_ADDRESS_HIGH                           |    |

| Table 10-30: MSI_ADDRESS_INGIT<br>Table 10-39: MSI_DATA |    |

| Table 10-99. MSI_DATA                                   |    |

| Table 10-41: PCIE_VEXT_ID                               |    |

| Table 10-42: PCIE_CAPABILITY                            |    |

| Table 10-43: PCIE_DEVICE_CAP                            |    |

| Table 10-44: PCIE_DCR                                   |    |

| Table 10-45: PCIE_DSR                                   |    |

| Table 10-46: PCIE_LINK_CAP                              |    |

| Table 10-47: PCIE_LCR                                   |    |

| Table 10-48: PCIE_LSR                                   |    |

| Table 10-49: DSN_CAP                                    |    |

| Table 10-49. DSN_CAT                                    |    |

| Table 10-50: DSN_LOW                                    |    |

| Table 10-51: VC_CAP                                     |    |

| Table 10-52: VC_CAI                                     |    |

| Table 10-53: VC_PORT_CAP_1                              |    |

| Table 10-54: VC_PCR                                     |    |

| Table 10-55: VC_PCR                                     |    |

| Table 10-50: VC_PSK<br>Table 10-57: VC_RESOURCE_CAP0    |    |

| Table 10-57: VC_RESOURCE_CAPU                           |    |

| Table 10-59: VC_RESOURCE_SR0                            |    |

| Table 10-59. VC_RESOURCE_SKU                            |    |

| Table 10-00. VC_RESOURCE_CAPT                           |    |

| Table 10-01. VC_RESOURCE_CK1                            |    |

| Table 10-02. VC_RESOURCE_SK1                            |    |

| Table 10-05: PCI_515_CPG_5151EM                         |    |

|                                                         |    |

| Table 10-65: CLK_CSR                                    |    |

| Table 10-66: PCI_BAR_CONFIG                             |    |

| Table 10-67: INT_CTRL                                   |    |

| Table 10-68: INT_STAT                                   |    |

| Table 10-69: PEX_ERROR_STAT                             |    |

| Table 10-70: INT_CFG0-7                                 |    |

| Table 10-71: PCI_TO_ACK_TIME                            |    |

| Table 10-72: PEX_CDN_CFG1                               |    |

| Table 10-73: PEX_CDN_CFG2                               |    |

| Table 10-74: PHY_TEST_CONTROL    |       |

|----------------------------------|-------|

| Table 10-75: PHY_CONTROL         |       |

| Table 10-76: CDN_LOCK            |       |

| Table 10-77: TWI_CTRL            |       |

| Table 10-78: TWI_STATUS          |       |

| Table 10-79: TWI_ADDRESS         |       |

| Table 10-80: TWI_DATA            |       |

| Table 10-81: TWI_IRT_STATUS      |       |

| Table 10-82: TWI_TR_SIZE         |       |

| Table 10-83: TWI_SLV_MON         |       |

| Table 10-84: TWI_TO              |       |

| Table 10-85: TWI_IR_MASK         |       |

| Table 10-86: TWI_IR_EN           |       |

| Table 10-87: TWI_IR_DIS          |       |

| Table 10-88: GPIO_BYPASS_MODE    |       |

| Table 10-89: GPIO_DIRECTION_MODE |       |

| Table 10-90: GPIO_OUTPUT_ENABLE  |       |

| Table 10-91: GPIO_OUTPUT_VALUE   |       |

| Table 10-92: GPIO_INPUT_VALUE    |       |

| Table 10-93: GPIO_INT_MASK       |       |

| Table 10-94: GPIO_INT_MASK_CLR   | . 152 |

| Table 10-95: GPIO_INT_MASK_SET   |       |

| Table 10-96: GPIO_INT_STATUS     |       |

| Table 10-97: GPIO_INT_TYPE       | . 155 |

| Table 10-98: GPIO_INT_VALUE      | . 156 |

| Table 10-99: GPIO_INT_ON_ANY     | . 157 |

| Table 10-100: FCL_CTRL           |       |

| Table 10-101: FCL_STATUS         | . 159 |

| Table 10-102: FCL_IODATA_IN      | . 159 |

| Table 10-103: FCL_IODATA_OUT     |       |

| Table 10-104: FCL_EN             | . 160 |

| Table 10-105: FCL_TIMER_0        | . 161 |

| Table 10-106: FCL_TIMER_1        | . 161 |

| Table 10-107: FCL_CLK_DIV        | . 162 |

| Table 10-108: FCL_IRQ            | . 162 |

| Table 10-109: FCL_TIMER_CTRL     | . 163 |

| Table 10-110: FCL_IM             | . 163 |

| Table 10-111: FCL_TIMER2_0       | . 164 |

| Table 10-112: FCL_TIMER2_1       | . 164 |

| Table 10-113: FCL_FIFO_DATA      | . 164 |

|                                  |       |

# List of Acronyms

| Acronym        | Description                                                      |  |

|----------------|------------------------------------------------------------------|--|

| АРВ            | Advanced Peripheral Bus                                          |  |

| ASPM           | Active State Power Management                                    |  |

| BAR4           | Base Address Registers                                           |  |

| DSNC (DSN_)    | Device Serial Number Capability                                  |  |

| FCL (FCL_)     | FGPA Configuration Loader                                        |  |

| FIFO           | First In First Out                                               |  |

| FPGA           | Field-Programmable Gate Array                                    |  |

| FSM            | Finite State Machine                                             |  |

| GPIO           | General Purpose Input Output                                     |  |

| LPVC           | Low-Priority Virtual Channel                                     |  |

| MSI (MSI_)     | Message Signalled Interrupt                                      |  |

| PCIEC (PCIEC_) | PCI Express Capability                                           |  |

| PEX            | PCI Express Digital Core with PIPE and Generic Transaction Layer |  |

| PM (PM_)       | Power Management                                                 |  |

| RCB            | Read Completion Boundary                                         |  |

| SPRI (SPRI_)   | Serial Programming Interface                                     |  |

| TBD            | To Be Defined                                                    |  |

| TWI (TWI_)     | 2-wire interface                                                 |  |

| UR             | Unsupported Request                                              |  |

| VC (VC_)       | PCI Express Virtual Channel Capability                           |  |

# List of References

| Reference Number | Reference Title                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| [1]              | PCI Express™ Base Specification Revision 1.1, PCI-SIG, March 28, 2005                                                |

| [2]              | Inter Integrated Circuit (I <sup>2</sup> C) Technical Data Sheet, Cadence, I-IPA01-0045-TDS Rev 11,<br>February 2007 |

| [3]              | The I <sup>2</sup> C-bus Specification, Philips Semiconductor, Version 2.1, January 2000                             |

| [4]              | Configuration Handbook, Altera, 1.4, October 2007                                                                    |

| [5]              | Spartan-3 Generation Configuration User Guide, Xilinx, UG332 (v1.2) May 23, 2007                                     |

| [6]              | The 3.3V Configuration of Spartan-3 FPGAs, XAPP453 (v1.1) April 3, 2006                                              |

### **GN412x PCI Express Family Reference Manual**

# 1. Introduction

For the past decade, PCI has been a dominant interconnect for both PC and embedded systems. With the shift to high-speed serial interfaces, PCI Express<sup>®</sup> is quickly replacing parallel PCI. As a leader in providing solutions for high-speed serial communications, Gennum has developed the GN412x family of PCI bridge controller components to complement FPGA devices. The GN412x family, comprised of the GN4124 and GN4121, is specifically designed to take advantage of the architectural features of low-cost FPGA devices that do not have PCI Express capable SerDes on-chip. The result is a low-cost bridging solution for high-performance native PCI Express bridging.

The GN412x is also desirable companion to PCIe capable FPGA devices, where the requirement for firmware upgrading and on-the-fly reconfiguration are required.

The GN4124 is a x4-lane PCI Express to local bus bridge and the GN4121 is a single lane variant. Both devices in the family are designed to work as a companions for FPGA devices to provide a complete bridging solution for general applications. In addition to a PCI Express compliant PHY interface (x4-lane in the case of the GN4124 and x1-lane for the GN4121), the GN412x devices contain the link and transaction layers, and an applications interface that is ideally suited to FPGA interfacing using a small number of pins.

Since the PCI Express transaction/link IP is hard-wired into the GN412x, there is no need to license PCIe IP. The level of integration and very low power operation of the GN412x make it an ideal alternative to using a PIPE PHY, where IP licensing and the cost of FPGA resources and power consumption is unattractive by comparison. Using the GN412x, allows FPGA resources to be spent on what differentiates the product, rather than on implementing the PCI Express protocol.

### 1.1 Features

- 4 Lane PCI Express interface for GN4124 OR 1 Lane PCI Express interface for GN4121

- Complies with PCI Express Base Specification 1.1

- On-chip PHY, transaction, and link layer eliminates the cost of IP licensing

- Two hardware virtual channels supported by the GN4124 (the GN4121 provides a single hardware virtual channel)

- Payload size of up to 512 bytes with up to three outstanding transactions in each direction per virtual channel

- Supports 3x64-bit base address registers

- Provides flexible power management capability

- Provides pin efficient local bus interface for easy attachment to popular low-cost FPGA devices

- Uses DDR SSTL I/O for high-speed local bus data transfer (up to 800MB/s for the GN4124 and 500MB/s for the GN4121)

- FPGA source code provided for 64-bit master/target read/write buses for easy user logic attachment

- Local bus may be operated asynchronously to the PCIe clock rate for power optimization

- "Live" on power up

- On-chip type 0 PCI configuration space enables auto detection without FPGA activity

- On-chip extended configuration space supports power management, serial number, MSI, and PCIe capability registers

- FPGA bitstream loader

- Allows easy configuration of the attached FPGA through PCIe

- Provides on-the-fly FPGA reconfiguration capability

- 2-wire master/target

- Boot master mode allows PCI configuration space defaults to be loaded from a small EEPROM upon system reset

- General master mode allows attached 2-wire devices to be read/written

- Target mode allows internal registers to be accessed from an external circuit or processor

A simplified block diagram of the GN412x chip is shown in Figure 1-1.

#### Figure 1-1: GN412x with FPGA Simplified Block Diagram

### **1.2 Live on Power-up**

Since the GN412x contains a complete type 0 PCI configuration space, it is live on power-up so that a plug-and-play BIOS can auto-detect it and enumerate it without an attached FPGA having to be configured.

## **1.3 FPGA On-the-Fly Configuration Loader**

An FPGA bitstream may be downloaded from the host system over PCIe to the attached FPGA using the on-chip FPGA configuration loader. This eliminates the expense of a dedicated FPGA ROM and makes on-the-fly reconfiguration and firmware upgrades simple. The ability to dynamically configure an attached FPGA over PCIe makes the GN412x an ideal companion to all ranges of FPGA devices, including large SerDes capable devices, that require reconfiguration or firmware upgrades over PCIe.

## **1.4 Local Bus Interface**

The local bus interface uses a combination of single and dual data rate SSTL I/O to accomplish very high data rates in the fewest possible pins. A singe data rate clock is used for SSTL control signals and separate dual data rate source synchronous clocking is used for the DDR SSTL data. The SDR control signals operate at up to 200MHz (125MHz for the GN4121) and the DDR I/O operate at up to 400MT/s across (250MT/s for the GN4121) 16 bits using a 200MHz (125MHz) DDR clock. This provides 800MB/s in each direction for the GN4124 and 500MB/s in each direction for the GN4124.

The local bus may operate asynchronously from the PCI Express rate. In order to save power, the local bus clock can operate at the lowest possible rate required by an application.

The local bus protocol facilitates four types of transactions:

- PCIe-to-Local Target Writes: A PCIe agent (such as the host processor/root complex) writes data to the local bus.

- PCIe-to-Local Target Reads: A PCIe agent reads data from the local bus. Reads are split into a request phase (address phase) and a completion phase (data phase).

- Local-to-PCIe Master Writes: The attached FPGA writes data to a PCIe device (such as host memory via a root complex).

- Local-to-PCIe Master Reads: The attached FPGA reads data from a PCIe device.

The PCIe-to-Local transactions would typical involve a target controller implemented in the FPGA. Local-to-PCIe Master transactions allow a DMA controller in the FPGA to access PCI Express devices.

## **1.5 Virtual Channel Support**

The GN4124 has two independent virtual channels that support the eight PCIe defined traffic classes. This enables high local bus utilization by supporting non-blocking traffic between virtual channels. This is accomplished with separate on-chip buffering resources for each of the two virtual channels. For example, when write buffering is full for VC0 and VC1 has room, then VC1 traffic may proceed without reference to the state of VC0. The GN4121 can only support VCO in hardware, even though VC1 related registers are available for the sake of software compatibility.

Virtual channels may be used to separate different types of application traffic. For example, a DMA engine in the FPGA may be aggressively reading and writing host memory to stream video data. At the same time another agent in the FPGA may need to communicate low bandwidth, latency sensitive synchronization information. If the two types of traffic are segregated in terms of virtual channels and traffic classes, then the low latency traffic can be allowed to pass the high bandwidth traffic.

# **1.6 PCI Express Application Layer**

The on-chip applications layer transfers data between the PCI Express port and an attached FPGA using the local bus interface. It provides a mechanism to access internal registers through configuration space access and through one of the Base Address Registers (BAR4). The applications layer supports the transmission of message signalled interrupts.

## **1.7 Interrupt Controller**

A flexible interrupt controller automatically generates PCIe message signalled interrupts from either external pins (GPIO pins) or internally generated interrupt sources. The interrupt controller can route any interrupt source to up to four GPIO pins.

# **1.8 2-Wire Serial Controller**

An on-chip I<sup>2</sup>C compatible controller provides both a master and target mode. After device reset, default configuration register values, such as Subsystem Vendor ID and BAR sizes, can be automatically loaded from a small serial EEPROM. After initialization, an external 2-wire master can access on-chip registers to read/write them.

**Note:** The GN4121 device supports one virtual channel.

### 1.9 How to Use this Family Reference Manual

The GN412x Family Reference Manual includes detailed information on GN412x-based systems programming and design. However, there are other complementary documents to assist designers available on the Gennum Web site: www.gennum.com/mygennum. A complete set of documentation includes the following:

- GN4124 Data Sheet (Document ID: 48407) OR GN4121 Data Sheet (Document ID: 51239)

- GN412x PCI Express Family Reference Manual (this document)

- GN4124 Master List of Documents & Electronic Files (Document ID: 52423) OR GN4121 Master List of Documents & Electronic Files (Document ID: 52571), which provides a summary of the content of the documentation, to help navigate the content

- Reference Design Kit (RDK) board and the asssociated documentation

Following chapters detail the operation of the major functional blocks inside the GN412x:

- 3. Initialization

- 4. PCI Express Link

- 5. Local Bus Interface

- 6. Interrupt Control Unit

- 7. Peripherals

- 8. FPGA Configuration Loader

- 9. Device Application

- 10. Internal Registers

Before finalizing a system design based on the GN412x, please contact Gennum to verify that you have the most recent specifications.

Gennum is constantly trying to improve the quality of its product documentation. If you have any questions or comments, please contact Gennum Technical Support.

### **1.9.1 Family Reference Manual Conventions**

Throughout this document, references to the GN412x may be applied to either of the devices and indicate that they operate the same. Where there is information specific to one or the other of the devices, the specific device (GN4124 or GN4121) will be named.

The GN412x can act as either a "requester" or "completer". A requester is a device that first introduces a transaction sequence into the PCI Express domain. In legacy PCI, this would equate to a "bus master" and a completer would be the equivalent of a "bus target".

In this document, PCIe master and PCIe requester may be used interchangeably. Similarly, completer and target may also be used interchangeably.

In documenting and labelling cycles and transactions, the following conventions are used:

- In general, transactions are specified as requester followed by completer. Therefore, a PCIe-to-local write is a transaction where a requester device, attached to the GN412x, transmits a write request to the GN412x that results in a write cycle on the local bus. Since all local bus writes are posted, there is no response at the local bus level<sup>1</sup>.

- A read transaction happens in two steps: the read request initiated by the requester, followed by the read completion initiated by the completer. This is also referred to as a split transaction<sup>2</sup>.

#### **1.9.1.1 Numbering Conventions**

Throughout this data sheet, hexadecimal numbers will use a 0x prefix. Multiple bits represented as binary will be shown in double quotes as in "1010" while single quotes will be used to denote single binary bits (either '1', or '0').

Unless otherwise noted, little endian conventions will be used. Consequently, the binary value "1000" represents bit 3 ='1' and bits 2 down-to 0 = '0'.

The following numbers are the same value:

• Example: Decimal 165 = 0xA5 = "10100101"

Binary numbers may use "X" to represent "don't care" bits:

• Example: "101X" represents both "1010" and "1011"

#### 1.9.1.2 Data Units

In keeping with PCI tradition, a 32-bit quantity will be referred to as a DW (double word) or alternately as a 32-bit word. Similarly, a 64-bit quantity may be referred to as a QW (quad word) or a 64-bit word.

<sup>1.</sup> PCIe write requests are acknowledged below the application layer. Consequently, there is no need to generate any response to write cycles at the local bus level.

<sup>2.</sup> A split transaction is a single logical transfer containing an initial transaction (the Request) terminated at the target (the Completer), followed by one or more transactions initiated by the Completer in response to the Request.

#### 1.9.1.3 Register Naming Conventions

Each register in the GN412x is given a mnemonic label. In each register, each bit and bit field are also given a mnemonic. A register bit or bit field is fully identified as: REGISTER.BITFIELD where REGISTER refers to the mnemonic of the register and BITFIELD refers to a bit or bit field inside the register.

### 1.10 Getting Help from Gennum

For technical support, contact Gennum by telephone or e-mail. E-mail ensures the quickest response. The most up-to-date technical support information is also posted on the Gennum website. E-mail: vbapps@gennum.com.

## **1.11 Getting Answers to PCI Express Related Questions**

This data sheet assumes a basic understanding of the PCI Express Specification. If you are looking for a copy of the specification please contact the PCI Special Interest group at 503-619-0569 or visit their Web site at: http://www.pcisig.com.

If you are not familiar with the PCI Express specification, a good place to start is by reading one of several books on the subject. One of the most popular is PCI Express System Architecture written by Tom Shanley, Don Anderson, and Ravi Budruk (published by MindShare Inc.).

# 2. Overview

A block diagram of the GN412x is depicted in Figure 2-1.

Each of the internal blocks is described in detail in the following chapters. They are:

- The PCI Express link is described in 3. PCI Express Link. This includes a description of the PCI Express related configuration registers.

- The Local bus is described in 4. Local Bus Interface.

- The interrupt controller is described in 5. Interrupt Control Unit.

- The boot master mode of the 2-wire controller is described in 3.1.3 Initialization from a 2-Wire EEPROM.

- General purpose master/target mode of the 2-wire controller is described in 7.1 2-Wire Interface.

- General purpose IO are described in 7.2 General Purpose IO Block.

- Details of all the internal registers and their respective register bit fields are described in 7. Internal Registers.

### 2.1 GN412x Signals

Figure 2-2 depicts the signals of the GN412x laid out in their logical groupings.

Note for GN4121 device, there is a reduction in pins, as a result L\_WR\_RDY[1:0] becomes L\_WR\_RDY, P\_RD\_D\_RDY[1:0] becomes P\_RD\_D\_RDY, P\_WR\_REQ[1:0] becomes P\_WR\_REQ, P\_WR\_RDY[1:0] becomes P\_WR\_RDY, VC\_RDY[1:0] becomes VC\_RDY, PETp[3:0] becomes PETp, PETn[3:0] becomes PETn, PERp[3:0] becomes PERp, and PERn[3:0] becomes PERn.

# 3. Initialization

Initialization of the GN412x usually occurs when the system is reset. The GN412x is reset when the RSTIN signal is driven active LOW. When RSTIN is later de-asserted, the GN412x's internal registers can be initialized via the PCI Express bus, an attached 2-wire<sup>1</sup> EEPROM, or from a processor through the 2-wire interface. This chapter describes reset options and register initialization procedures.

There are two types of initialization to be discussed:

- Reset initialization: Initialization that happens after reset is released and before the PCIe BIOS or host operating system interacts with the GN412x.

- OS initialization: Initialization that happens after reset initialization when the PCIe BIOS or host operating system interacts with the GN412x.

### **3.1 Reset Initialization**

The GN412x chip is reset by driving active (LOW) the **RSTIN** pin. For a PCIe Endpoint application, **RSTIN** is driven from the **PERST** (PCI Express Reset bar) signal of the PCIe connector. RSTIN doesn't have to be synchronous to any particular clock and is relatively immune to noise spikes due to its high level of input hysteresis.

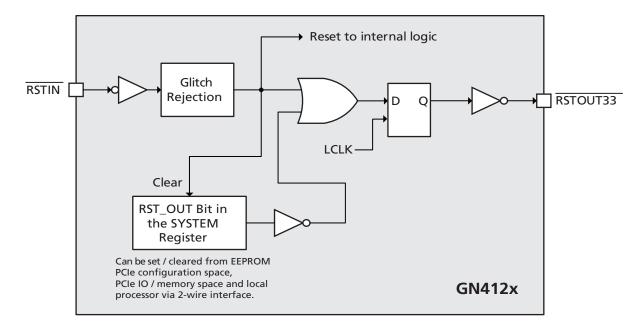

Reset input and output operation is depicted in Figure 3-1.

#### Figure 3-1: Reset Input and Output Operation

<sup>1.</sup> The 2-wire interface is compatible with the  $I^2C$  specification.  $I^2C$  is a trademark of Koninklijke Philips Electronics NV.

### **3.1.1 Initializing the Internal Registers**

There are three options for initializing the GN412x internal registers set after reset:

- Initialization from the 2-wire serial EEPROM interface.

- Initialization from the PCIe bus side via configuration space.

- Initialization from the 2-wire interface by an external 2-wire master.

### 3.1.2 Selecting an Initialization Mode

In order to support Plug-and-Play operation, an endpoint device must provide configuration space information back to the host operating system so that it knows which drivers to load. Since the GN412x may be used in multiple applications from multiple vendors, the default configuration space settings would not allow each application variant to be uniquely identified. In order to provide unique application dependant configuration space settings, some of the defaults must be overwritten. This will include at least the Subsystem Vendor ID and Subsystem ID. These registers will allow an operating system to determine the driver to load during the "OS initialization" phase.

There are three reset initialization modes that can be selected. These are shown in Table 3-1.

| EEPROM Port<br>Connection                                          | EEPROM_EN<br>State | Bits in PCI_SYS_CFG_SYSTEM<br>Register |             | STEM Comment                                                                                                                                                                                          |

|--------------------------------------------------------------------|--------------------|----------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    |                    | CFG_RETRY                              | RST_OUT     | _                                                                                                                                                                                                     |